eProcessor

eProcessor at HiPEAC 2022

June 28, 2022

eProcessor in Hannover Messe 2022

June 3, 2022

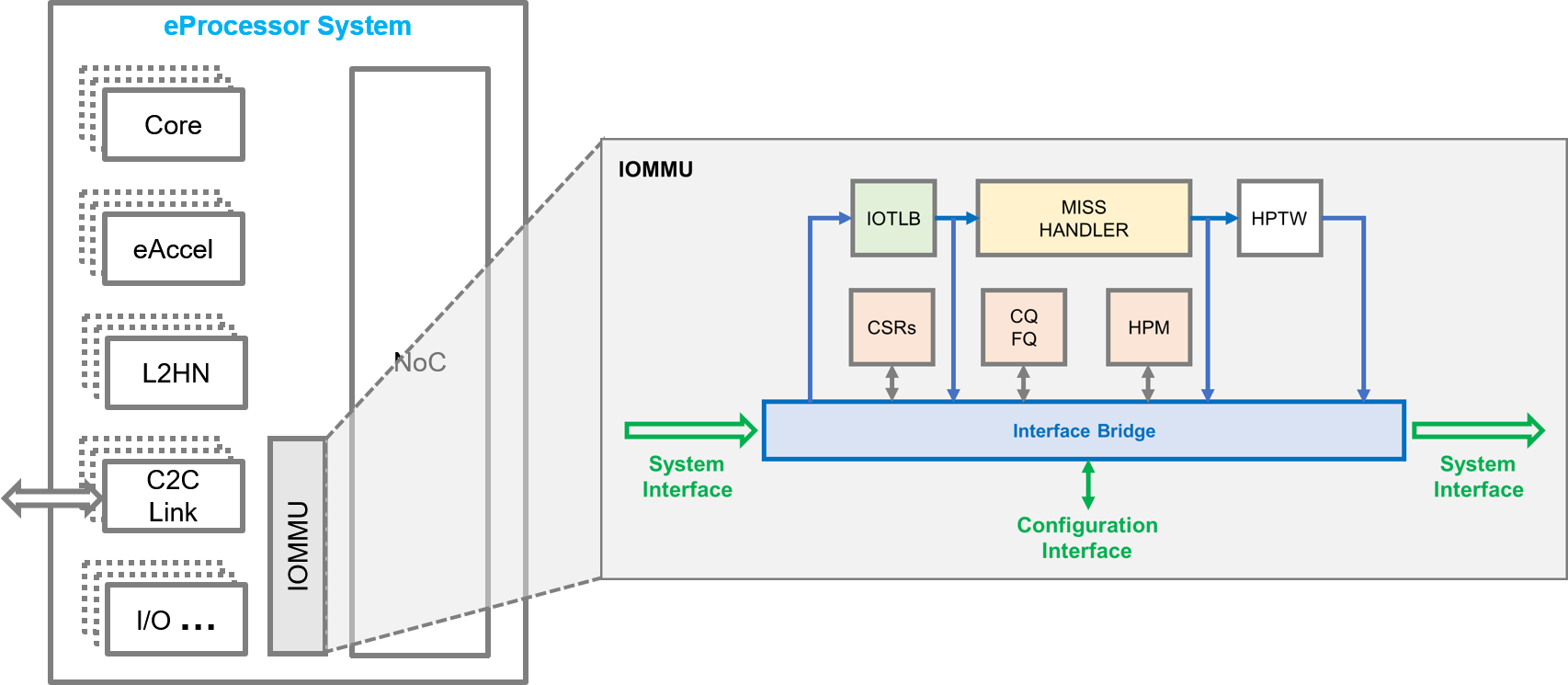

The RISC-V IOMMU of eProcessor in a Nutshell

May 17, 2022

eProcessor presented in Sparcity project

November 11, 2021

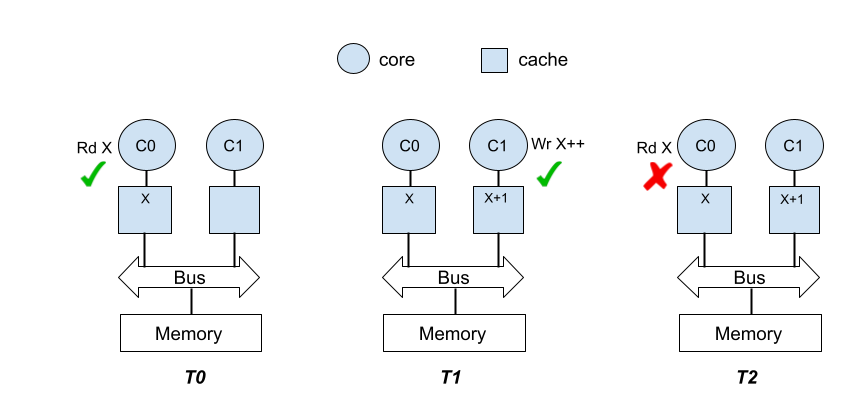

eProcessor cache coherence in a Nutshell

October 8, 2021